FET #

The field effect transistor is a device whose working is depends upon the control of current by an electric field, hence field effect transistor.

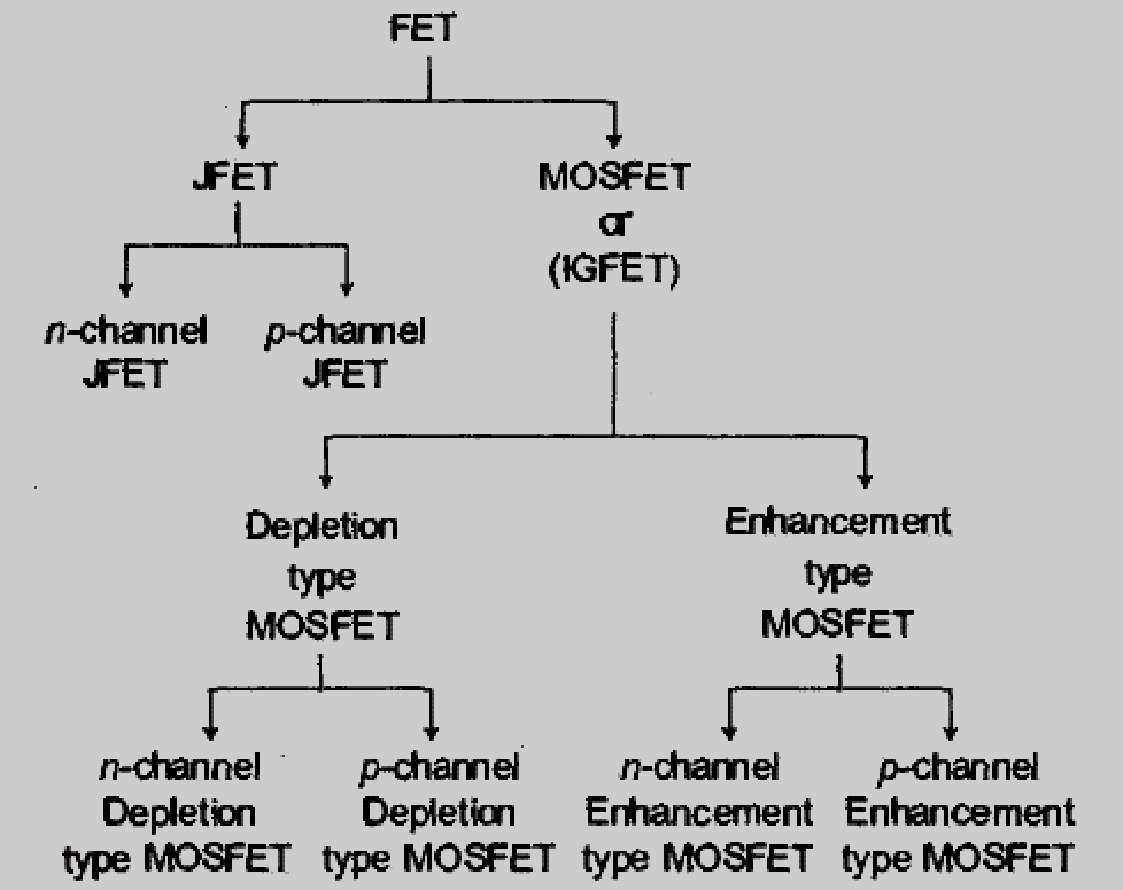

There are two types of field-effect transistors:

- Junction field effect Transistor (JFET)

- Insulated gate field effect transistor (IGFET) also known as metal-oxide semiconductor transistor (MOSFET).

Classification of FET #

Comparison between FET and BJT #

|

FET |

BJT |

|---|---|

|

1. FET is an unipolar semiconductor device because its operation depends upon the flow of majority carriers i.e., either holes or electrons as the case may be. |

1. BJT is a bipolar semiconductor device because the current constituting elements are both majority carriers as well as minority carriers in this case. |

|

2. The input impedance of FET is much larger (ranging in Magaohms) than BJT. The reason behind this is that the input terminal i.e., gate to source of FET is reverse biased and reverse bias offers ideally infinite resistance. |

2. The input impedance of BJT is very less in comparison to FET. |

|

3. FET is a voltage controlled device. |

3. BJT is a current controlled device. |

|

4. FET is less noisy. Because there are no junctions. |

4. Much noisy than FET. |

|

5. Higher frequency response. |

5. Frequency variation effects the performance. |

|

6. Good thermal stability because of absence of minority carriers. |

6. Temperature dependent thermal runaway may occur. |

|

7. Costlier than BJT. |

7. Relatively cheaper. |

|

8. Smaller in size. |

8. Comparatively bigger. |

|

9. In FET, relationship between input and output quantities is nonlinear due to square term in Shockley’s equations

|

9. The BJT is an almost linear device or we can say that BJT works linearly in active region as an amplifier. |

|

10. No offset voltage; so it works better as a switch or chopper |

10. There is always an offset voltage before switching. |

|

11. Small gain bandwidth product. |

11. Greater than FET. |

Terminal analogy of FET and BJT

|

BJT |

Collector (C) |

Base (B) |

Emitter (E) |

IC |

VCE |

|---|---|---|---|---|---|

|

FET |

Drain (D) |

Gate (G) |

Source (S) |

ID |

VDS |

JFET BJT

- Construction of JFET: (n-channel JFET)

Source: The source is the terminal through which the majority carriers enter the bar. Conventional current entering the bar at S is designated by

Drain: It is the terminal through which the majority carriers leave the bar. Conventional current entering the bar at D is designated by .

The drain to source voltage is called and is positive if D is more positive than S.

Gate: It is the heavily doped () region on both sides of the n-type bar formed by allowing, by diffusion, or by any other procedure available for creating p-n junction.

Between the gate and source a voltage is applied in the direction to reverse bias the p-n junction. Conventional current entering the bar at G is designated by

Channel: The region of n-type material lies between the two gate regions is the channel through which the majority carriers move from source to drain.

Note:

If channel is n-type then Gate will be p-type OR If channel is p-type then Gate will be n-type.

Circuit Symbols of JFET

n- Channel JFET p- Channel JFET

Water Analogy for control Mechanism of JFET working

FET Characteristics #

Drain Characteristics #

It is the relationship between at constant.

Ohmic Region #

The region is shown as a curve OA in fig. In this region, the drain current increases

linearly with the increase in drain-to-source voltage, obeying Ohm’s law. The linear

increase in drain current is due to the fact that n-type semi-conductor bar acts like a

simple resistor.

Curve AB

In this region, the drain current increase at the reverse square law rate with the increase in drain-to-source voltage. It means that drain current increases slowly as compared to that in ohmic region. It is because of the fact, that with the increase in drain-to-source voltage, the drain current increases. This in turn increases the reverse bias voltage across the gate-source junction. As a reuslt of this, the depletion region grows in size, there by reducing the effective width of channel. At the drain-to-source voltage, corresponding to point B, the channel width is reduced to a minimum value and is known as pinch off. The drain-to-source voltage, at which the channel pinch-off occurs, is known as pinch off voltage (VP).

Pinch Off region

This region is shown by the curve BC. It is also called saturation region or constant current region. In this region, the drain current remians constant at its maximum value (i.e., IDSS). The drain, current in the pinch off region, depends upon the gate-to-source voltage and is given by the relation,

The above relation is known as Shockly’s equation.

The pinch off region is the normal operating region of JFET, when used as an amplifier.

Breakdown Region

This region is shown by the curve CD. In this region, the drain current increases rapidly as the drain-to-source voltage is also increased. It happens because of the breakdown of gate-to-source junction due to avalanche effect. The drain-to-source voltage corresponding to point C is called breakdown voltage.

Following are the possible cases

Case 1: When VGS = 0 and VDS = 0. In this condition the drain current is zero.

Case 2: When VGS ![]() 0 and VDS = 0. Under this condition pn-junction being reverse biased and increases the width of the depletion layer. Now, if VGS is increased more negatively then the situation of pinch off occurs. At this instant, IDmax also decreases because channel becomes narrower due to reverse bias.

0 and VDS = 0. Under this condition pn-junction being reverse biased and increases the width of the depletion layer. Now, if VGS is increased more negatively then the situation of pinch off occurs. At this instant, IDmax also decreases because channel becomes narrower due to reverse bias.

Case 3: When VGS = 0 and VDS > 0, i.e., a positive voltage Vos has been applied across the channel. The gate and source are connected directly, i.e., VGs = 0. In this situation ID = IS (i.e., VDS = VDD). Under this condition the flow of charge is relatively uninhabited and limited only by the resistance of the n-channel between drain and source.

Note:

As shown in the diagram given below, the depletion layer is wider near drain side as compared to source side because when current flows in silicon bar, there occurs a voltage drop across the channel along whole length due to the reverse bias voltage across the drain and the gate is comparatively much larger than the reverse bias voltage across the gate and source.

Difference between ohmic and Saturation Region #

|

SN |

FET |

BJT |

|---|---|---|

|

1. |

– ID varies in proportion with VDS |

– ID is almost constant irrespective of change in VDS |

|

2. |

– FET acts as Voltage Variable Resistor (VVR) or voltage Dependent Resistor (VDR) |

– FET acts as a controlled current source |

|

3. |

– Here the FET work as a switch |

– Here the FET work as an amplifier |

|

4. |

– Power dissipation is low in this region |

– Power dissipation is high in this region |

Transfer Characteristics

The Transfer Characteristics of JFET is governed by the current and voltage equation as given below:

OR

Where ID = Drain current

IDSS = Saturated (max) value of drain current

VGS = Gate to source voltage (i.e., control variable)

VP = Pinch-off voltage

Transfer and drain Characteristics of n-type JFET #

Pinch-off voltage #

As we have already discussed that if the magnitude of reverse bias voltage is applied to gate is increased sufficiently, drain current ID becomes zero. This situation of JFET operation is known as pinch-off.

To understand the concept of pinch-off voltage is very necessary. It can be better understand by the fig. shown below:

Above discussion reveals that when gate to source voltage (VGS) approaches to pinch off voltage (i.e., VP), drain current (ID) becomes zero, but in fact it is not so. This can be easily understood by the mathematical relation of drain current:

ID = A ND ![]() E

E

or ID = 2b (x) w ND ![]() E

E

(Area A = 2b (x). W, VDS = E × L)

Where, ID = Drain current

2b(x) = Effective channel width

w = Depletion region width

ND = Doping concentration

= Mobility of electron

= Mobility of electron

E = Applied electric field

L = Length of the channel

q = Charge of the electron (or hole)

i) Relation between Pinch off Voltage () , doping concentration () and

Channel width (a) is given by:

Where, VP = pinch-off voltage

ND = Doping concentration

a = Channel width

ii) Relation between Pinch off Voltage () , Gate to Source Voltage () and Channel width (a) is given by #

VGS = Gate-to-source voltage

VP = Pinch of voltage

a = Channel width

b = Effective channel width.

Low Frequency Small signal Model of JFET

id = gm VGS +

Where, gm =

is the mutual conductance or transconductance. It is often referred to as common source forward transmittance.

The second parameter rd in equation (F) is the drain resistance or output resistance and is defined by

i.e. rd is the inverse ratio of change in drain voltage to change in drain current at constant gate to source voltage.

JFET Parameters #

AC drain Resistance #

It is defined as the ratio of change in drain to source voltage ( ![]() VDS) to change in drain current (

VDS) to change in drain current ( ![]() ID) at constant gate to source voltage and is denoted by rd

ID) at constant gate to source voltage and is denoted by rd

It is also known as dynamic drain resistance.

Transconductance #

It is also known as forward transmittace. Generally, it is expressed in mA/volt or micro- Siemens.

When ID, the drain current gets saturated i.e., attains the value of IDSS, then gm denoted by gmo. Transconductance tells us how effective the gate-source voltage is in controlling the drain current.

The higher the value of transconductance means that the gate is more effective in controlling the drain current.

Realtion between and #

#

where gmo is the value of transconductance with VGS = 0

As per the Shockley’s equation.

or

or gm =

Substituting VGS = 0 in above expression then

![]()

or

Note:

The quantity VGS(off) is difficult to measure accurately. For this reason, VGS(off) is often calculated with the following equation.

Amplification-factor #

Amplification factor is defined as the ratio of change in drain to source voltage to the change in gate to source voltage at constant drain-current. It is denoted by ![]()

Relation between Amplification-factor , transconductance (), and drain-resistance)

Relation between amplification factor, transconductance and drain-resistance, we have amplification factor,

Amplification factor is defined as the ratio of change in drain to source voltage to the change in gate to source voltage at constant drain-current. It is denoted by ![]()

Amplification factor is defined as the ratio of change in drain to source voltage to the change in gate to source voltage at constant drain-current. It is denoted by ![]()

Thus, amplification factor = ac drain resistance × transconductance.

DC Drain to Source Resistance ()

It is also called as the static or ohmic resistance of the channel and is defind as ratio of drain to source voltage and drain-current ID. It is represented by RDS.

Construction of MOSFET #

n-channel depletion MOSFET #

Drain and Transfer Characteristics of n-type depletion MOSFET

P-channel depletion MOSFET #

Drain and Transfer Characteristics of P-type depletion MOSFET

n-channel enhancement MOSFET #

Drain and Transfer Characteristics of n-type enhancement MOSFET

Circuit Symbol

FET as an amplifier #

BJT as an amplifier have 3 configurations (i.e CE, CB, CC) in the same way the FET’s as an amplifier have 3 configurations (i.e Common Drain, Common Source, Common Gate) as given below:

Generalized FET amplifier configuration #

From the above configuration if output is taken from the drain (D) i.e., V01 it is called common-source (CS) amplifier, however if the output is taken from the source (S) i.e., V02 it is called common-drain (CD) or the source follower (analogous to the emitter follower or common collector configuration for a bipolar junction transistor).

Small signal equivalent circuit of FET Amplifier

idRd + (id – gmVGS)rd + idRs = 0 … (1)

Also, VGS = Vi – idRs … (2)

Combining equation (1) and (2) and using ![]() = rdgm

= rdgm

We have

Case 1. The CS amplifier with an un-by-passed source resistance.

From fig. (a) V01 = – idRd, then we have

… (3)

… (3)

From equation (3), we obtain the Thevenin’s equivalent circuit of fig. given under here

Equivalent circuit for the generalized FET amplifier when output is taken from the drain.

Voltage gain (AV):

AV = ![]()

AV =

…(4)

…(4)

Note: Here the minus sign in equation (4) indicates that out is 180o out of phase with the input.

If RS is bypassed with a large capacitance or if source is grounded, the above relation in equation (4) is valid with Rs = 0 under this situation voltage gain becomes.

AV =  (

( ![]() RS = 0)

RS = 0)

Where, ![]() = gmrd and R’d = Rd || rd

= gmrd and R’d = Rd || rd

Output resistance (R0): #

Case II. Common drain (CD) or source follower with drain resistance.

From fig. (a), we have

V02 = idRS

V02 =

… (5)

… (5)

From equation (5), we obtain the Thevenin’s equivalent circuit as in given fig. working into the source. In this equation, the open circuit voltage is  and the output resistance is R0 =

and the output resistance is R0 = ![]() .

.

The voltage gain is A0 =  . There is no phase shift between input and output.

. There is no phase shift between input and output.

If Rd = 0 and if (![]() + 1) RS > rd then

+ 1) RS > rd then

Equivalent circuit for the generalised FET amplifier

When output taken from the source.

Hence for source follower with Rd = 0 and ![]() >> 1

>> 1

R0 =

or R0 = ![]() (Rd = 0,

(Rd = 0, ![]() >>1)

>>1)

or R0 = ![]()

or

Note

Unity voltage gain means that the output (at the source) follows the input (at the gate). Hence, the CD configuration is called a source follower (analogous to the emitter follower for a BJT amplifier).

- Small signal model for the MOSFET: (hybrid )

High- Frequency Model of MOSFET

Important Formulae

(i)gm =

=

(ii) r0 = ![]()

(iii) Cgs = ![]() WLCox + WL Cox

WLCox + WL Cox

(iv) Cgd = WLCox

(v) Csb = ![]()

(vi) Cdb =

(vii) fT =  e

e

The figure of Merit for the high frequency operation of the MOSFET as an amplifier is the unity-gain frequency fT.

fT is defined as the frequency at which short circuit current gain of the common-source configuration becomes unity.

Summary of different configurations of FET

Common –Source:

Important Formulae:

Common –Source with source resistance:

Common- Gate:

Common drain or Source Follower

Avs =

Comparison Between JFET and MOSFET #

- JFETs can only operate in the depletion mode whereas MOSFETs can be operated in either depletion or en enhancement mode.

- MOSFET have much higher input impedance than that of JFETs. This is duet o negligible small leakage current.

Comparison of p-channel and n- channel device #

|

SN |

Particular |

n-channel |

p-channel |

|---|---|---|---|

|

1. |

Nature of charge carriers. |

In an n-channel JFET the current carriers or change carries are electrons. |

Here, charge carriers are holes. |

|

2. |

Mobility of the charge carriers. |

Mobility of electrons in n-channel is higher. |

The mobility of holes in p-channel devices is lower. |

|

3. |

Noise. |

They are less noisy. |

They are more noisy than n-channel |

|

4. |

Transconductance |

Larger |

Smaller |

|

5. |

Manufacturing Process. |

Its manufacturing process is very difficult. |

Its manufacturing process is comparatively easy. |

Difference between Ohmic and Saturation Region #

|

SN |

Ohmic region |

Saturation region |

|---|---|---|

|

1. |

– ID varies in proportion with VDS |

– ID is almost constant irrespective of change in VDS |

|

2. |

– FET acts as a Voltage Variable Resistor (VVR) |

– FET acts as a controlled current source |

|

3. |

– Here the FET work as a switch |

– Here the FET work as an amplifier |

|

4. |

– Power dissipation is low in this region |

– Power dissipation is high in this region |

Summary of FET biasing: #

|

Configuration |

Z1 |

Z0 |

|

|---|---|---|---|

|

Fixed-bias [JEET or D-MOSFET]

|

High = |

Medium

|

Medium (– 10)

|

|

Self-bias bypassed Rs [JEET or D-MOSFET]

|

High = |

Medium

|

Medium (– 10)

|

|

Self-bias unbypassed Rs [JFET or D-MOSFET]

|

High = |

|

Low (– 2)

|

|

Voltage-divider bias [JFET or D-MOSFT]

|

High = |

Medium

|

Medium (– 10)

|

|

Source-follower [JFET or D-MOSFET]

|

High = |

Medium

|

Low (< 1)

|

|

Common-gate [JFET or D-MOSFET]

|

Low

|

Medium

|

Medium (+ 10)

|

|

Drain-feedback bias E-MOSFET

|

Medium

|

Medium

|

Medium (– 10)

|

|

Voltage-divider bias E-MOSFET

|

Medium

|

Medium

|

Medium (– 10)

|

|

Configuration |

|

Z0 |

Z1 |

|---|---|---|---|

|

|

Including rd

|

RG RG |

RD

|

|

|

Including rd

|

RG RG |

|

|

|

Including rd

|

R1||R2 R1||R2 |

RD RD||rd |

|

|

Including rd

|

RG RG |

|

|

|

Including rd

|

|

RD RD||rd |