Digital Design Flow #

Introduction #

- IC: Integrated Circuits, many transistors on one chip

- VLSI: Very Large Scale Integration, a modern technology of IC design flow the term vlsi is used to collectively refer to many fields of electrical and computer engineering that deal with the analysis and design of very dense is a vlsi chip contains more than 106 switching devices or logic gates early in the first decade of the 21″ century, the actual number of transistors has exceeded 108 on a silicon die of typically 1 cm2 area=

System on chip #

- Design methodology and knowledge change significantly from one component to the other!! System-on-Chip

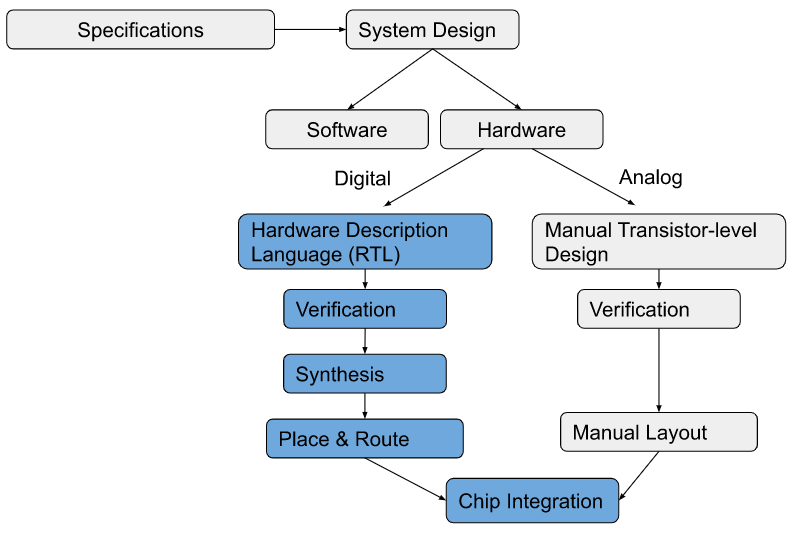

Top-Down System Design Flow #

RTL Based Chip Design Flow #

Top-level requirements

- This step specifies the top-level goal of the ICwith the top-level constraints under which this goal has to be achieved

- Functionality of the design (design objective)

- Speed at which a design can operate (design constraint

- Power consumed by the design (design constraint)

- Testability of the design (design objective)

- Area of chip package (design constraint)

Micro-Architecture

- This step specifies the detailed design in terms of hardware blocks and software components of the IC

Design creation

- For new blocks, RTL design is created and blocks (IPs)identified to be reused are sourced either in-house or from IP vendor

RTL analysis

- All the blocks are verified using static analysis (i.e., not needing test vectors) tools to detect and fix the issues carly

Functional verification

- A mix of cycle-based simulation (on test vectors) and formal verification (property based checking) is used to ensure that RTL design meets Nodes (i| represent states

- Arcs (i,)) represent transitions from i to j

- Each arc(i,]) is labeled with

- a Boolean expression f, which

- only depends on input signals

- and define the transition

- condition.

- Output signal values,the intended functionality

Synthesis

- Based on timing, power and area constraints, the RTL of all the blocks are synthesized into netlist (cells or macros) for targeted technology.

Netlist analysis

- Generate netlist is verified to ensure that it still meets the top-level requirements. This is done using formal equivalence with RTL, gate-level simulation, power analysis and static timing analysis etc.

Design For Test (FT)

- Netlist is post-processed for test requirements e.g. replacing normal flops with scan flops building scan chains, Scan-tacing to verify scan chains, etc

Backend phase

- This phase consists of various steps e.g. placement and routing (P&R), performing all the verifications again on P&R nellist (functional, timing, power, test, area, etc) and various other finishing activities. Finally, the fabricated chip is then tested on a tester machine and delivery is made to the market.

ASIC vs. FPGA Flow #

Digital Design Tradeoffs

![]()

![]()

- Chips are fabrication

For a specific circuit

- Application Specific ICs

(ASICs)

Standard Cell Design Strategy #

- ASIC design is based on a library of pre-designed and characterized digital cells for a specific fabrication technology.

- Utilized for smaller production ASICs that are automatically generated by synthesis tools

- Library development is a time-consuming and difficult task that must be repeated for every technology generation

- From where to get the library:

- Available from Library vendors/foundries, and qualified at defined foundries

- Some ASIC manufacturers (foundries) sell their own library. Layout is often in phantom cells (empty boxes filled at foundry).

- Build your own library and characterize it: Only large companies.

- Provide a large library for better synthesis performance

- More cells slows down the synthesis tool, which must compare all alternatives.

Standard Cells #

- Provide a large library of logic cells

- Deeper stacking and complex functians slows down the circuit, so use simple logic gates

- A0132, NAND4, NOR4, XOR2, Majority,

- Storage elements

- latch, F/F, embedded logic, reset, scan

- Multiplexers, Adders, Half-Adders

- Sophisticated libraries also generate memories of assorted sizes from a

- Deeper stacking and complex functians slows down the circuit, so use simple logic gates

graphical user interface

-

- 1/O pads.

- Can be several hundred cells

- Drive a variety of loads: Usually designers provide different ” flavors” of the same gate (binary weighting: x1,x2.x4. x8.k16)

- Each provide: Symbal, Behavior, Netlist & Layout

Field-Programmable Gate Arrays-FPGAS #

- Basic idea: two-dimensional array of logic blocks and flip-flops with a means for the user to configure (program):

- The function of each block (CLB: Configurable Logic Block)

- The interconnections between the logic blocks (PSM: Programmable Switch Matrices)

- Technical viewpoint:

- For hardware/system-designers, just like ASICs, only better

- Fabricate a new chip every few hours

- Re-configurability

- In-field Re-programmability

- At the expense of

- Performance (speed), Area and Power.

- Versus ASICs: delay 3-4X, area 40X, and power 12X l!

Idealised CLB

- 4-input look up table (LUT)

- implements combinational logic functions

- Register

- optionally stores output of LUT

State Transition Diagram/Table

- Natural way to think of a FSM

- Collection of states and transition arcs

- States are labeled with state name and outputs

- Arcs are labeled with input condition/outputs

- In this small example

- States named “S 1″”S2″”S3”

- Inputs are “a””b”

- Outputs are “x”””y”

- A clear, concise, and visual way to describe a machine

- Forms good documentation of HDL code

| Current | Input | Next | Output |

|---|---|---|---|

| S1 | b | S2 | x |

| S2 | a+b | S2 | y |

| S2` | a’b’ | S3 | x |

| S3 | a | S1 | y |

State Transition Table

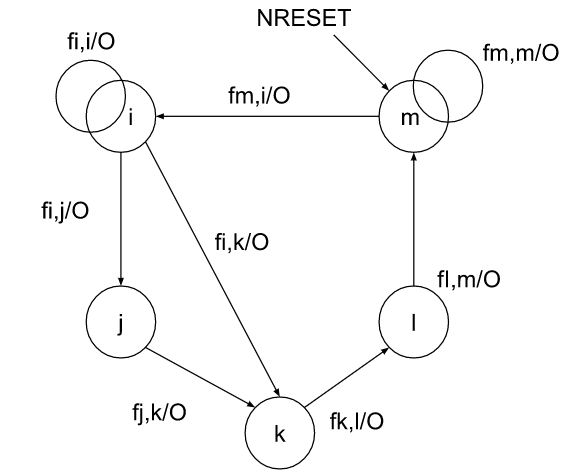

Graphical Representation – Mealy

- Nodes {i} represent states

- Arcs (i,j) represent transitions from i to j

- Each arc(i,j) is labeled with

- a Boolean expression f, which only depends on input signals and define the transition condition.

- Output signal values,O

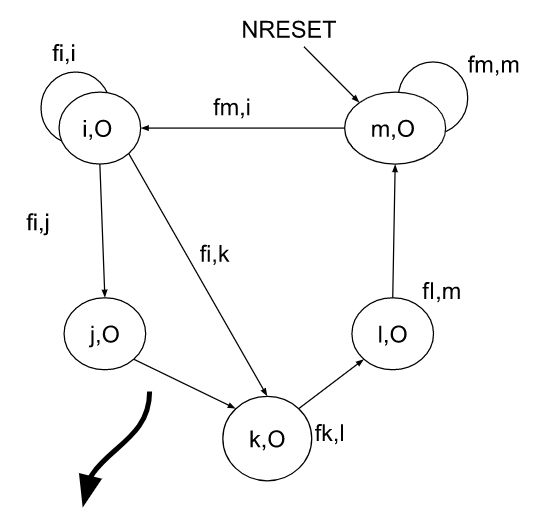

Graphical Representation – Moore

- Nodes {i} represent states

- Arcs (i,j) represent transitions from i to j

- Each arc(i,j) is labeled with

- a Boolean expression fi, which only depends on input signals and defines the transition condition.

- Output signals, O, only depend on the state. Each node is also labeled with the output signal values.

- An arc with no label indicates that state transition will occur at the next clock cycle.

Universal Verification Methodology (UVM) #

System Verilog is a language just like Verilog and has its own constructs, syntax and features

but UVM is a framework of SystemVerilog classes from which fully functional testbenches can be built. There’s only one prerequisite to learn UVM, and that is SystemVerilog because it is the

foundation for the tower that is UVM

Why?

The primary advantage is that the methodology specifies and lays out a set of guidelines to be

followed for creation of verification testbenches. This will ensure testbench uniformity between

different verification teams, cross-compatibility between IP and standalone environment

integration, flexibility and ease of maintaining testbenches

How does UVM help? #

Every verification testbench has a few key components like drivers, monitors, stimulus generators and scoreboards. UVM provides a base class for each of these components with standardized functions to instantiate, connect and build the testbench environment. These are static entities called components in a verification environment that exist throughout a simulation just like buildings in a city. These components operate and process on some kind of data that flows around the environment similar to people and vehicles in the city. The data or transactions are called objects or sequence items since they appear and disappear at various times in the simulation and is more dynamic in nature.

UVM-Architecture #